## TG3: Analog Electronics for Ge detectors

Goal of Task Group: Delivery of

- Front-end (FE) circuts for Ge det. read-out

- Cables from FE to FADC

- HV-PS, LV-PS, Pulser

• Slow-control of operational parameters of digital and analog electronics.

#### Status of TG3 works: FE not ASIC cryogenic circuits

|                                                                                                                                                      | Status /<br>meet specs | Date               | Notes                                                               |

|------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|--------------------|---------------------------------------------------------------------|

| Test of FE Circuit 1<br>(AGATA, discrete<br>components)                                                                                              | Achieved               | 09/05              | Discrete components.<br>Warm outside LN bath<br>with cold FET       |

| Test of FE Circuit 2<br>(IPA4 – monolithic JFET+<br>polarizing components)<br>Production of 20 FE<br>channels for Ge<br>prototypes at LNGS and<br>MU | Achieved<br>Achieved   | 02/2005<br>05/2006 | Semi-integrated.<br>Polarizing components, CF,RF<br>not integrated. |

| Test of produced channels                                                                                                                            | To be done             | 07/2006            |                                                                     |

| Test of FE circuit 3<br>(AMPTEK- A250)                                                                                                               | $\checkmark$           | 12/2005            | Ibrid can work at cryo-T.                                           |

GERDA meeting 26-28 June 2006

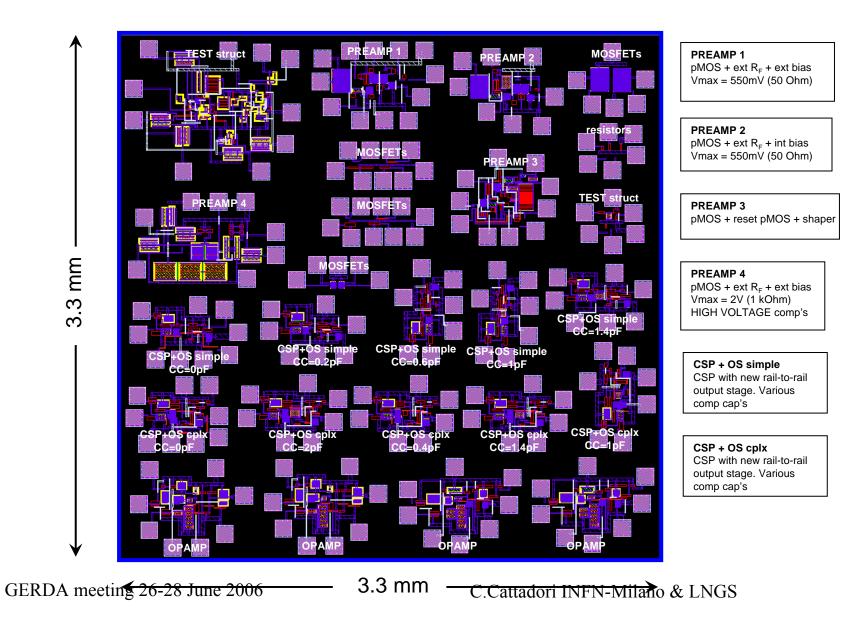

# Status of TG3 works: ASIC FE cryogenic circuits

| MI- ASIC – CMOS FE                |            |                | Integrated but not CF,RF     |

|-----------------------------------|------------|----------------|------------------------------|

| Test                              | Achieved   | 06/2005        |                              |

| Test of chips                     | Achieved   | 12/2005        |                              |

| 2 <sup>nd</sup> run (fine tuning) | To be done | 10/2006        |                              |

| Production                        | To be done | 2007           |                              |

| MI- ASIC – CMOS FE                |            |                | Fully Integrated but not RF, |

| Test run                          | Submitted  | 07/2006        | with possible active reset   |

| Test of chips                     | TBA        | 09/2006        |                              |

| 2 <sup>nd</sup> run (tuning)      | TBA        | 10/2006        |                              |

| Packaging                         | Candidate  | 04/2006        |                              |

| Hd ASIC-CMOS                      |            |                | Fully integrated             |

| Test run                          | Done       | 02/2006        |                              |

| Test of chips                     | TBA        | ?              |                              |

| 2 <sup>nd</sup> run               | TBA        | ?              |                              |

| Production                        | TBA        | 2007           |                              |

| ERDA meeting 26-28 June 2006      | 1          | C.Cattadori II | NFN-Milano & LNGS            |

|                                                                                              | Status /<br>meet specs                | Date               | Notes                                                                      |

|----------------------------------------------------------------------------------------------|---------------------------------------|--------------------|----------------------------------------------------------------------------|

| HV for Ge detector<br>Caburn Kapton 8 kV<br>0,25 mm diam                                     | Achieved                              | 06/05              | Measured by M.Laubenstein<br>< 10 mBq/kg both for U and<br>Th. (30 g/ 6 m) |

| Signal (from FE to<br>FADC) and LV PS<br>(picocoax-Axon)<br>(siltem coax)<br>(Tekdata woven) | X<br>Ongoing,<br>candidates<br>exists | 12/2005<br>05/2006 | To be measured γ-<br>spectrometry                                          |

| LV PS                                                                                        | Candidate                             | 07/2006            | INFN-PD design and production                                              |

| HV PS                                                                                        | Candidate                             |                    |                                                                            |

| Pulser                                                                                       | X                                     | 12/2006            |                                                                            |

#### Status of TG3 works : Cables (Phase I) and LV,HV PS

GERDA meeting 26-28 June 2006

# Possible problems

Too high radioactivity of components, as the junction box has to be put nearest the top of the crystal string compared to the showed solution (see talk of B.Majorovits)

# IPA4+external FET BF862: Why?

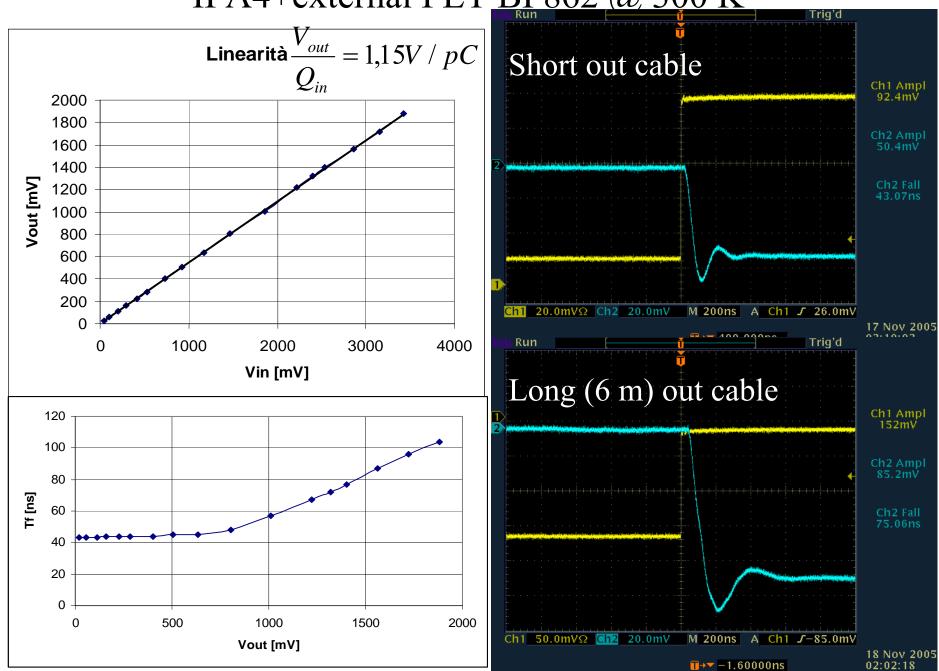

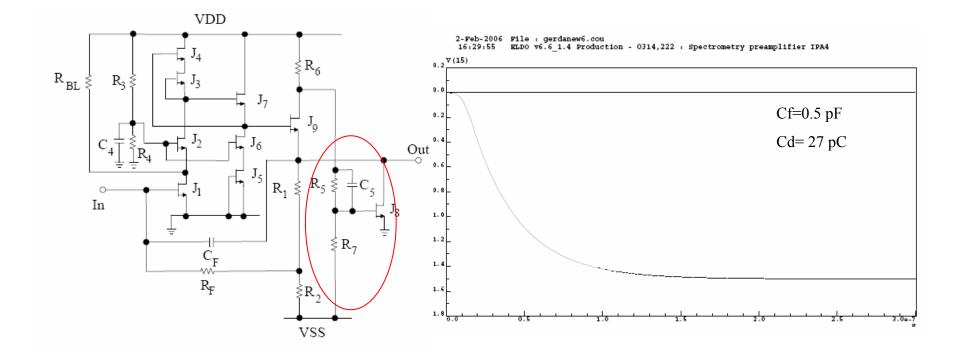

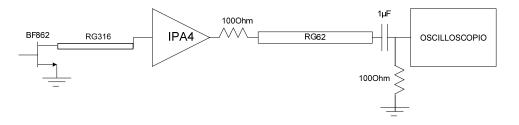

# IPA4+external FET BF862 @ 300 K

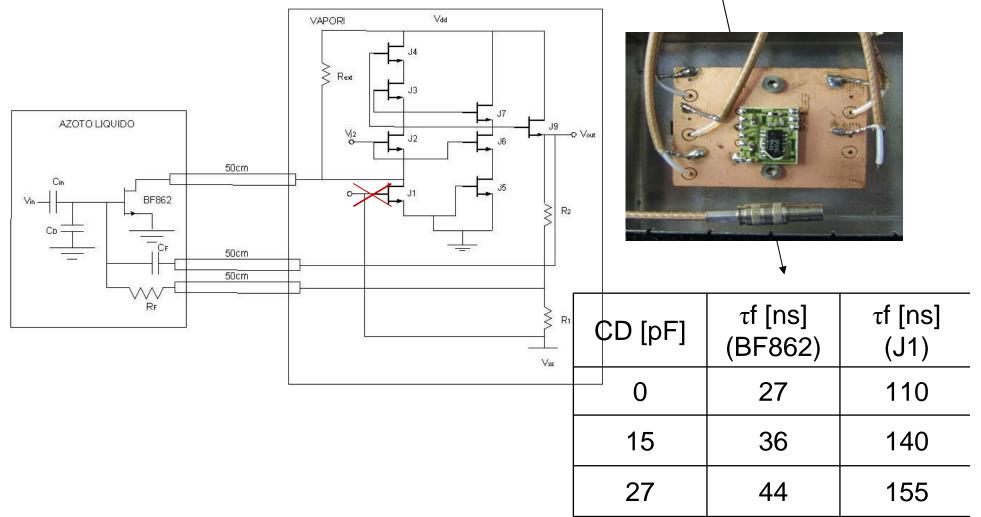

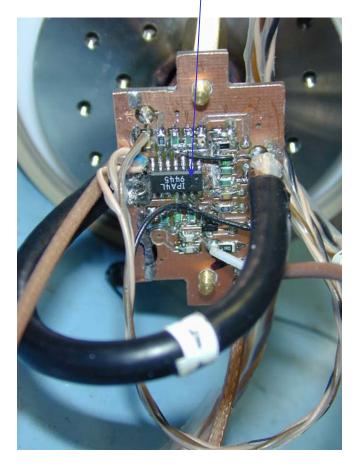

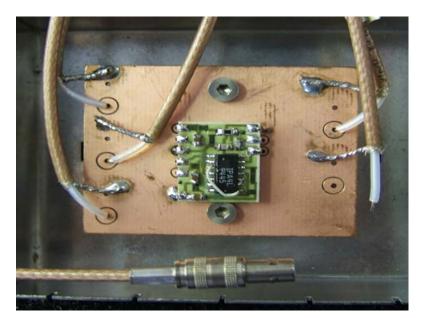

#### IPA4 + $J1_{ext}$ + 100 $\Omega$ Out stage: the new test board

New setup for LN measurements

GERDA meeting 26-28 June 2006

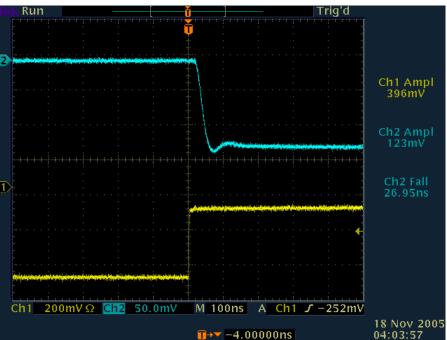

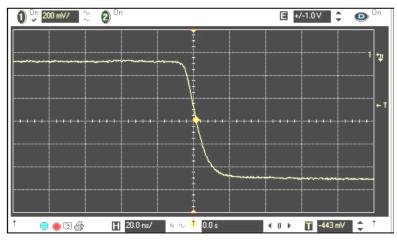

#### IPA4 + $J1_{ext}$ + 100 Out stage: simulated pulse 50 ns fall time (@ 300 K).

Swing to -1.5 V

#### IPA4 + $J1_{ext}$ + 100 $\Omega$ Out stage: the new test board

New setup for LN measurements

GERDA meeting 26-28 June 2006

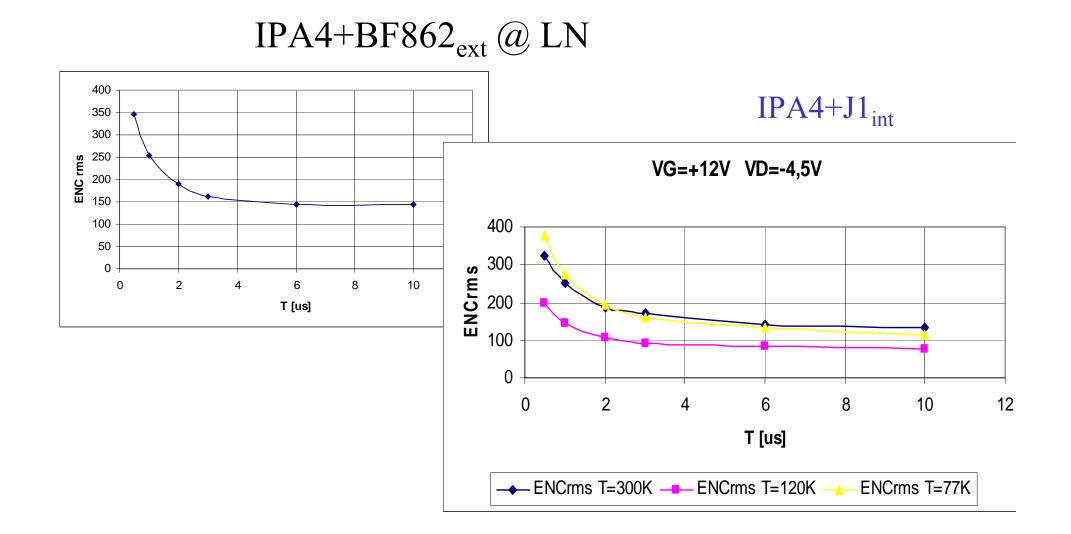

# Back to 1 k $\Omega$ out stage, better pulse shape

Measured pulse fall time for IPA4 preamp. Operated with integrated J1 or external BF862, at T=LN.

| CD [pF] | τf [ns]<br>(BF862) | τf [ns]<br>(J1) |

|---------|--------------------|-----------------|

| 0       | 27                 | 110             |

| 15      | 36                 | 140             |

| 27      | 44                 | 155             |

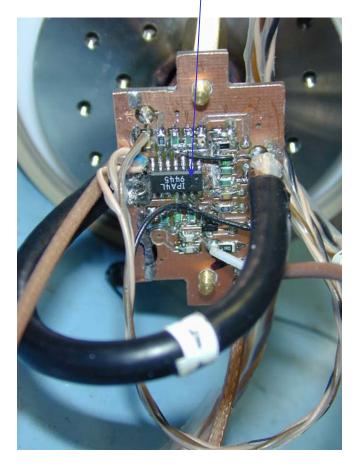

Production of 20 FE cryogenics circuits (based on IPA4 JFET monolithic circuit) for MU 18 fold segmented prototype, and for LNGS Phase I detector tests

Production of PCB: 23 june at AREL, without 100  $\Omega$  output stage: Lowest dissipation and not perfect shape

Mounting of components: this week (end 30 june provided I send components).

For LNGS test: 2-3 channels

For MU 18-fold crystal: test and mount circuits on mother board to host 20 preamps and signal-in signal-out. Ready to work endjuly.

IPA4+BF882 LC POS SCALA 1:1 08/05/06

IPA4+BF862 LC POS SCALA 1:1 08/05/06

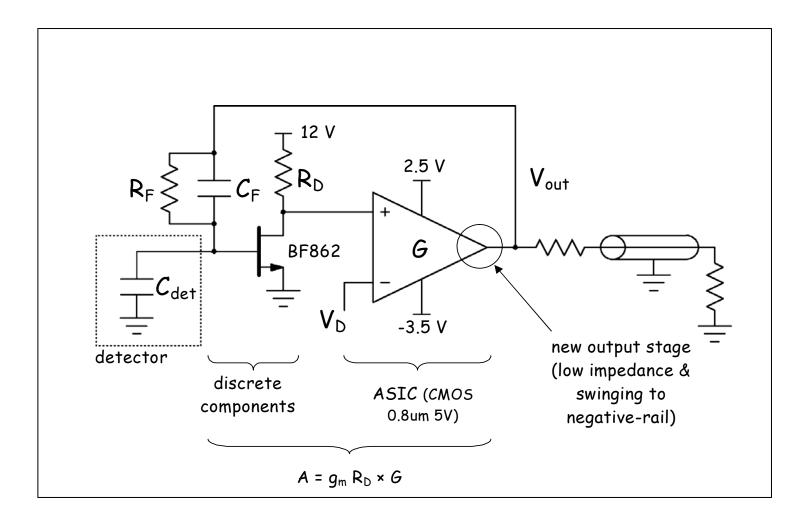

# Charge Preamplifier and Fully Differential Line Driver Integrated in AMS CMOS 0.8um CXZ Tech. for the GERDA Experiment

Milan University and I.N.F.N.

GERDA meeting 26-28 June 2006

# Input transistor

# External (JFET e.g. BF862)

- Noise <u>is</u> adequate

- Bandwidth is adequate

- Transistor <u>can</u> be replaced

- Can work at  $V_{GS} = 0$  V which helps zeroing the output offset

- Power consumption is high

### Integrated (p-MOSFET)

- Noise <u>could</u> be adequate

- Bandwidth is adequate

- Transistor <u>cannot</u> be replaced

- Transistor cannot work at V<sub>GS</sub> = 0

V

- Power consumption of p-MOSFET could be lower

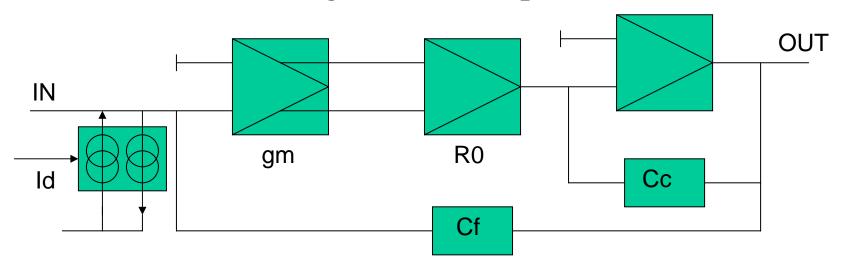

#### Proposed circuit structure (from J. Gal\*)

# Test chip

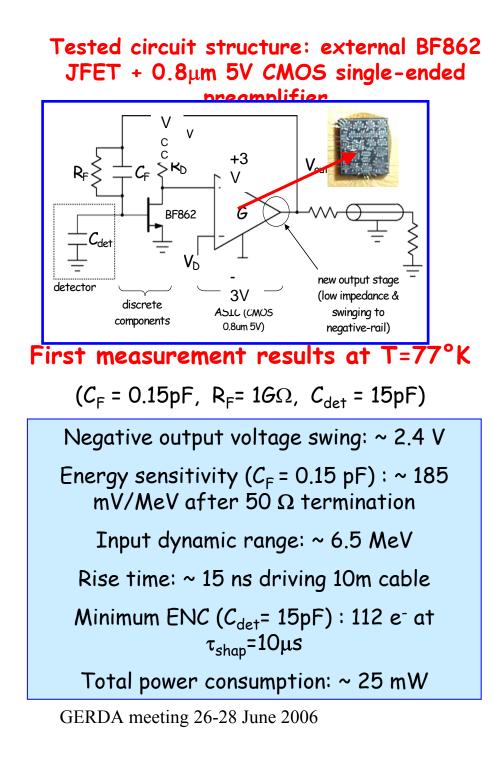

#### Acquired output signal driving a 50 $\Omega$ coaxial cable of ~ 10 m : rise time of ~ 15 ns

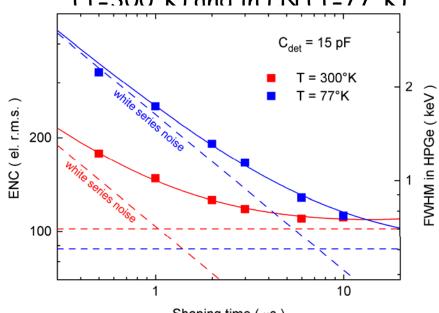

Comparison between **noise measured** at room temperature (T=300°K) and in LN (T=77°K)

### **Integrated Preamplifier**

- Tunable system (variable gm and R0 by a factor of 10)

- Noise, bandwidth according to specifications

- Dual Power Supply (+2.5v / -2.5v) / No additional Vrefs required

- Fully Bipolar Output Swing (+1.6v / -1.6v) @ Rload = 1 Kohm

- Non linearity < 1/1000 @ (-1.6v < Output Swing < +1.6v)

- Can operate with continuous reset (external R) or pulsed reset (bipolar Id)

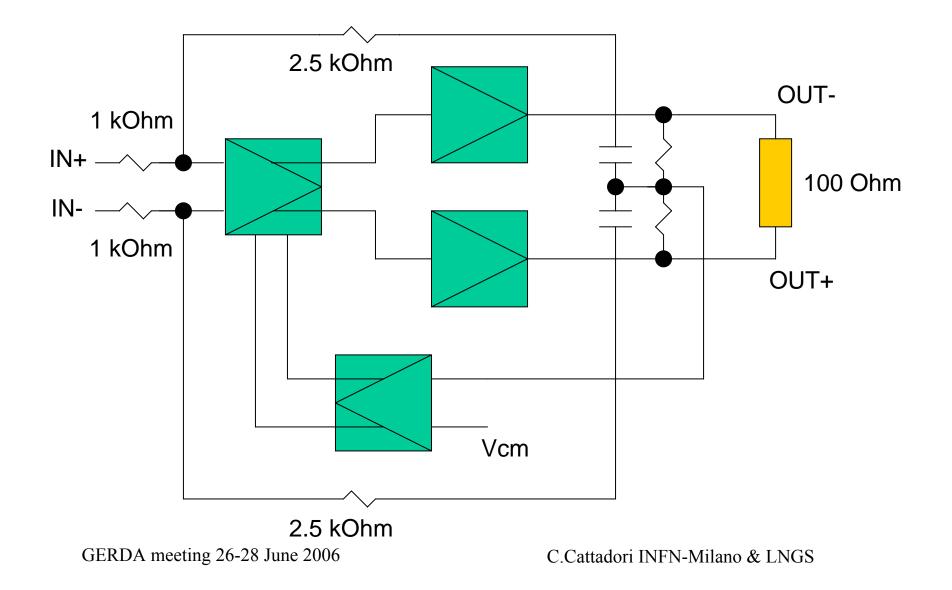

### Fully Differential Line Driver

## Fully Differential Line Driver

- Dual Power Supply (+2.5v/-2.5v)

- No additional Vrefs required

- Fully Differential Signal Path inside the OpAmp

- Fully Bipolar Output Swing (+2v/-2v) @ Rload = 100 Ohm

- Large Differential Output Swing (8v) @ Rload = 100 Ohm

- Bandwidth according to specifications

- Tunable system

- Variable Power Consumption: (from 3 mA @ Low Power up to 6 mA @ Full Bandwidth)

#### Low Voltage Low Noise PS designed at PD –INFN workshop V=+12 V, V=+5 V, V=-5 V, I = 0.7 A each)

# If test OK then can be adopted for GERDA

GERDA meeting 26-28 June 2006